思泽远管家式售后服务 (让您省心放心)

5分钟内电话回访

2小时内报价

24小时在线服务

芯片设计流程

发布时间:2023-05-09 文章出自:思泽远科技

芯片设计,又称集成电路设计(Integrated circuit design, IC design),亦可称之为超大规模集成电路设计(VLSI design),是指以集成电路、超大规模集成电路为目标的设计流程。集成电路设计涉及对电子器件(例如晶体管、电阻器、电容器等)、器件间互连线模型的建立。所有的器件和互连线都需安置在一块半导体衬底材料之上,这些组件通过半导体器件制造工艺(例如光刻等)安置在单一的硅衬底上,从而形成电路。

芯片设计流程

一、总体规划

随着集成电路设计规模的不断扩大,出现了很多成熟的常用设计模块,也被成为IP核,现在芯片正向设计,不再是完全从0开始,都是基于某些成熟的IP核,并在此基础之上进行芯片功能的添加。芯片正向设计依然是从市场未来需求着手,从开发成本和预期收益来衡量是否进行芯片的开发的。明确市场未来需求之后,就将这些需求转化为芯片的各项重要参数指标,然后进行任务划分,模拟设计师负责模拟,数字设计师负责数字。

二、架构/算法

现在数字电路在芯片中占有极大的比重,数字逻辑也变得越来越复杂,所以必须从架构和算法上进行考虑。

架构可以分为三种大的方向:数据流;控制流;总线流。

1、数据流:数据从输入到输出是一条直线,并没有折回的数据,这是纯数据处理的一种架构,这种芯片功能应该是比较单一。

2、控制流:这是基于状态机或者CPU形式的一种架构设计。简单点的芯片就采用状态机就够了,复杂的就必须采用CPU作为控制内核了,比如单片机就是以CPU为控制内核,外加RAM,ROM所形成的一类控制类芯片。

3、总线流:这是基于总线的芯片设计架构,最熟悉的就是SOC类芯片,总线上连接着一个或多个CPU,RAM,ROM,I2C,UART等等之类的各种组件。由这些组件的不同排列组合,形成满足各种不同需求的芯片,例如不同的ARM类芯片。

三、RTL代码

当算法工程师把芯片架构设计好,各种算法在MATLAB上通过了验证,以及其他必要条件的考量之后,便将工作交接给ASIC工程师去做RTL代码的翻译工作,就是将MATLAB上的算法翻译成RTL。这一步单纯从翻译的角度只需要一个文本编辑器就可以了。然而,还有后续的仿真验证工作,这部分的内容并不轻松。有时候根据公司的不同,根据项目的工作量大小,算法工程师与ASIC工程师在工作内容上是有交叉的,他们也承担将MATLAB转换为RTL的工作。RTL设计的时候也会考虑DFT(Design For Test 可测性设计)的问题,会在RTL代码中加入测试链,这个我就不太熟了。

四、仿真验证

这一步的工作比较关键,可以说是设计部分的第一个分水岭。仿真验证,视不同的公司,不同的项目,复杂度有非常大的不同。简单的,只要写一个较为完善的testbench验证完RTL代码的功能就行了;复杂的,将会在RTL验证环境下进行详细的验证,甚至可能用得到各种验证方法学UVM,VMM,OVM等等,这种复杂验证所用的语言一般采用SystemVerilog。验证软件可以采用cadence公司的NC_VERILOG,或者synopsys公司的VCS。

五、工艺选择

正向设计在一开始的整体规划中就要考虑工艺的问题,这涉及到有关工艺的相关知识,有些工艺就是特别为某种类型的芯片而开发的。所以一旦是要开发某种有对应工艺的芯片,则直接采用即可,但往往工艺的选择会特别耗时间,会有各种参数的考量,例如工艺生产周期,工艺的成品率,工艺生产时间的安排等等各方面的考究。[2]

六、综合、时序&功耗分析

这部分的工作主要用到synopsys公司的工具Design Complier(综合)、Prime Time(时序和功耗)。这两个工具的使用比较复杂,使用说明参考百度文库相关资料。总体来说,这两个工具都是约束驱动型软件,软件在使用时都是靠约束文件来进行驱动的。所以工作的主要内容除了软件的使用外最重要的就在于如何编写约束文件。一般而言,约束主要有面积约束,扇入扇出约束,时序约束等约束条件。如果RTL代码不满足约束,则必须根据具体情况修改约束条件或者是修改RTL代码。约束条件是用TCL脚本语言来写。综合和时序分析会生成基于所采用的工艺的电路网表,这个网表将是下一步自动布局布线所用到的主文件。

七、 形式验证

形式验证是在每一次芯片的逻辑电路转换为另一种表达形式的时候都需要做的工作。具体来说,在综合生成网表后做一次,主要对比的文件为RTL仿真之后的文件和综合之后的网表,在布局布线之后还需要做一次,主要对比文件为综合之后的网表与布局布线之后的网表。

主要工作内容:

1、准备好待比较的两份文件及各种工艺技术库文件;

2、用TCL脚本编写脚本程序,设置其中一份文件为比较标准,其中一份为待比较文件;

3、运行Formality,分析生成的比较报告;

4、根据报告做出相应的调整与修改。

八、自动布局布线

这个步骤严重依赖于软件和经验,目前常用的软件为Cadence Encounter,Synopsys公司也有对应的自动布局布线的软件ASTRO。主要工作内容:1、准备好工艺文件(时序文件库 数字版图库);2,准备好综合之后的电路网表文件及约束文件;3,根据设计要求,设置好版图面积等相关参数,4,进行自动布局布线,检查时序和功耗。

最新新闻

思泽远15 年技术深耕,构建全品类语音芯片产品生态

作为一家集研发、生产、销售和服务为一体的高科技企业,思泽远科技从成立之初便聚焦语音芯片领域,凭借对音质的极致追求和对市场需求的敏锐洞察,逐步搭建起覆盖 “基础语音播放 - 录变音 - 智能识别 - 音频放大” 的全链条产品体系,为不同行业客户提供 “选型 - 开发 - 落地” 的一站式解决方案。

语音芯片在儿童玩具电子发声书方案应用

玩具发声书语音芯片方案以其独特的功能设计和广泛的应用场景,成为市场上备受欢迎的选择。轻松一点,知识响起,寓教于乐,从此开启孩子的声音探索之旅。

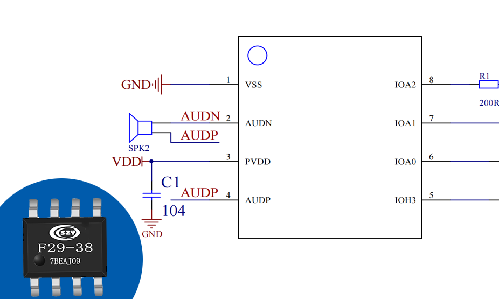

F29-38门铃音乐芯片介绍和ic电路图

思泽远科技的F29-38门铃音乐芯片是一款专为门铃设计的集成电路,旨在通过提供丰富多样的音乐播放功能,提升门铃的整体体验。这款芯片以其高集成度、低功耗以及灵活的定制性,在智能家居市场中占据了一席之地。

产品推荐

联系方式 · contact

联系电话: 137603272330755-29112251

专线负责人手机:+8613760327233( 吴经理 )

公司地址:深圳市宝安区西乡街道宝民二路河东大厦A座7楼7001-7009室

手机扫码进入网站

微信扫码沟通

Copyright © 2021 深圳市思泽远科技有限公司 版权所有 备案号:粤ICP备15066427号 Powered By HuahanLink

合作热线

0755-29112251

咨询热线

13760327233

微信扫码咨询

WhatsApp扫码

返回顶部